FN9009.6

#### Data Sheet

## Single Synchronous Buck Pulse-Width Modulation (PWM) Controller

intercil

The ISL6520 makes simple work out of implementing a complete control and protection scheme for a DC/DC stepdown converter. Designed to drive N-Channel MOSFETs in a synchronous buck topology, the ISL6520 integrates the control, output adjustment, monitoring and protection functions into a single 8 Lead package.

The ISL6520 provides simple, single feedback loop, voltagemode control with fast transient response. The output voltage can be precisely regulated to as low as 0.8V, with a maximum tolerance of  $\pm 1.5\%$  over-temperature and line voltage variations. A fixed frequency oscillator reduces design complexity, while balancing typical application cost and efficiency.

The error amplifier features a 15MHz gain-bandwidth product and  $8V/\mu s$  slew rate which enables high converter bandwidth for fast transient performance. The resulting PWM duty cycles range from 0% to 100%.

Protection from over-current conditions is provided by monitoring the  $r_{DS(ON)}$  of the upper MOSFET to inhibit PWM operation appropriately. This approach simplifies the implementation and improves efficiency by eliminating the need for a current sense resistor.

## Ordering Information

| PART<br>NUMBER        | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE                      | PKG.<br>DWG. # |  |

|-----------------------|-----------------|---------------------|------------------------------|----------------|--|

| ISL6520CB*            | 6520CB          | 0 to 70             | 8 Ld SOIC                    | M8.15          |  |

| ISL6520CBZ*<br>(Note) | 6520 CBZ        | 0 to 70             | 8 Ld SOIC<br>(Pb-free)       | M8.15          |  |

| ISL6520IB*            | 6520IB          | -40 to 85           | 8 Ld SOIC                    | M8.15          |  |

| ISL6520IBZ*<br>(Note) | 6520 IBZ        | -40 to 85           | 8 Ld SOIC<br>(Pb-free)       | M8.15          |  |

| ISL6520CR*            | ISL<br>6520CR   | 0 to 70             | 16 Ld 4x4mm QFN              | L16.4x4        |  |

| ISL6520CRZ*<br>(Note) | 65 20CRZ        | 0 to 70             | 16 Ld 4x4mm QFN<br>(Pb-free) | L16.4x4        |  |

| ISL6520IR*            | ISL 6520IR      | -40 to 85           | 16 Ld 4x4mm QFN              | L16.4x4        |  |

| ISL6520IRZ*<br>(Note) | 65 20IRZ        | -40 to 85           | 16 Ld 4x4mm QFN<br>(Pb-free) | L16.4x4        |  |

| ISL6520EVAL           | 1               | Evaluation Board    |                              |                |  |

\* Add "-T" suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### Features

- Operates from +5V Input

- 0.8V to VIN Output Range

- 0.8V Internal Reference

- ±1.5% Over Line Voltage and Temperature

- Drives N-Channel MOSFETs

- Simple Single-Loop Control Design

Voltage-Mode PWM Control

- Fast Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Cycle

- Lossless, Programmable Over-Current Protection

- Uses Upper MOSFET's rDS(on)

- Small Converter Size

- 300kHz Fixed Frequency Oscillator

- Internal Soft Start

- 8 Ld SOIC or 16Ld 4mmx4mm QFN

- QFN Package:

- Compliant to JEDEC PUB95 MO-220 QFN Quad Flat No Leads - Package Outline

- Near Chip Scale Package footprint, which improves PCB efficiency and has a thinner profile

- Pb-Free Plus Anneal Available (RoHS Compliant)

## Applications

- Power Supplies for Microprocessors

- PCs

- Embedded Controllers

- Subsystem Power Supplies

- PCI/AGP/GTL+ Buses

- ACPI Power Control

- · Cable Modems, Set Top Boxes, and DSL Modems

- DSP and Core Communications Processor Supplies

- Memory Supplies

- Personal Computer Peripherals

- Industrial Power Supplies

- 5V-Input DC/DC Regulators

- Low-Voltage Distributed Power Supplies

#### **Absolute Maximum Ratings**

| Supply Voltage, V <sub>CC</sub> +6.0V               |

|-----------------------------------------------------|

| Absolute Boot Voltage, VBOOT+15.0V                  |

| Upper Driver Supply Voltage, VBOOT - VPHASE         |

| 8.0V (<10ns Pulse Width, 10μJ)                      |

| Input, Output or I/O Voltage GND -0.3V to VCC +0.3V |

| ESD Classification Class 2                          |

### **Recommended Operating Conditions**

#### **Thermal Information**

| Thermal Resistance                | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------|------------------------|------------------------|

| SOIC Package (Note 1)             | 95                     | N/A                    |

| QFN Package (Notes 2, 3)          | 45                     | 7                      |

| Maximum Junction Temperature      |                        |                        |

| (Plastic Package)                 |                        | . +150°C               |

| Maximum Storage Temperature Range | 65°C                   | to +150°C              |

| Maximum Lead Temperature          |                        |                        |

| (Soldering 10s)                   |                        | . +300°C               |

| (SOIC - Lead Tips Only)           |                        |                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 2. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 3. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

| Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. |                         |                                |      |       |      |                  |

|-------------------------------------------------------------------------------------|-------------------------|--------------------------------|------|-------|------|------------------|

| PARAMETER                                                                           | SYMBOL                  | TEST CONDITIONS                | MIN  | TYP   | MAX  | UNITS            |

| VCC SUPPLY CURRENT                                                                  |                         |                                |      |       |      |                  |

| Nominal Supply                                                                      | IVCC                    | UGATE and LGATE Open           | 2.6  | 3.2   | 3.8  | mA               |

| POWER-ON RESET                                                                      |                         | ·                              |      |       |      |                  |

| Rising VCC POR Threshold                                                            | POR                     |                                | 4.19 | 4.30  | 4.5  | V                |

| VCC POR Threshold Hysteresis                                                        |                         |                                | -    | 0.25  | -    | V                |

| OSCILLATOR                                                                          |                         | ·                              |      |       |      |                  |

| Frequency                                                                           | fosc                    | ISL6520C, V <sub>CC</sub> = 5V | 250  | 300   | 340  | kHz              |

|                                                                                     |                         | ISL6520I, V <sub>CC</sub> = 5V | 230  | 300   | 340  | kHz              |

| Ramp Amplitude                                                                      | ΔV <sub>OSC</sub>       |                                | -    | 1.5   | -    | V <sub>P-P</sub> |

| REFERENCE                                                                           | I                       | 1                              | L    |       |      |                  |

| Reference Voltage Tolerance                                                         |                         | ISL6520C                       | -1.5 | -     | +1.5 | %                |

|                                                                                     |                         | ISL6520I                       | -2.5 |       | +2.5 | %                |

| Nominal Reference Voltage                                                           | V <sub>REF</sub>        |                                | -    | 0.800 | -    | V                |

| ERROR AMPLIFIER                                                                     |                         | I                              |      |       |      |                  |

| DC Gain                                                                             |                         | Guaranteed By Design           | -    | 88    | -    | dB               |

| Gain-Bandwidth Product                                                              | GBWP                    |                                | -    | 15    | -    | MHz              |

| Slew Rate                                                                           | SR                      | -                              | -    | 8     | -    | V/µs             |

| GATE DRIVERS                                                                        |                         | 1                              | L.   |       |      |                  |

| Upper Gate Source Current                                                           | IUGATE-SRC              |                                | -    | -1    | -    | А                |

| Upper Gate Sink Current                                                             | IUGATE-SNK              |                                | -    | 1     | -    | А                |

| Lower Gate Source Current                                                           | I <sub>LGATE</sub> -SRC |                                | -    | -1    | -    | Α                |

| Lower Gate Sink Current                                                             | I <sub>LGATE</sub> -SNK |                                | -    | 2     | -    | А                |

| PROTECTION / DISABLE                                                                | 1                       |                                |      |       |      |                  |

| OCSET Current Source                                                                | IOCSET                  | ISL6520C                       | 17   | 20    | 22   | μA               |

|                                                                                     |                         | ISL6520I                       | 14   | 20    | 24   | μA               |

| Disable Threshold                                                                   | VDISABLE                |                                | -    | 0.8   | -    | V                |

#### Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted.

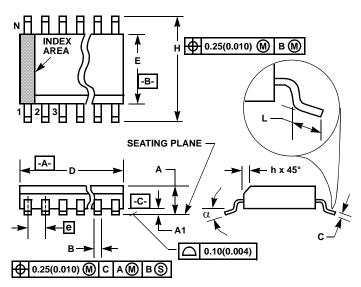

# Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

#### **M8.15** (JEDEC MS-012-AA ISSUE C) 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES    |        | MILLIMETERS |      |       |

|--------|-----------|--------|-------------|------|-------|

| SYMBOL | MIN       | MAX    | MIN         | MAX  | NOTES |

| Α      | 0.0532    | 0.0688 | 1.35        | 1.75 | -     |

| A1     | 0.0040    | 0.0098 | 0.10        | 0.25 | -     |

| В      | 0.013     | 0.020  | 0.33        | 0.51 | 9     |

| С      | 0.0075    | 0.0098 | 0.19        | 0.25 | -     |

| D      | 0.1890    | 0.1968 | 4.80        | 5.00 | 3     |

| E      | 0.1497    | 0.1574 | 3.80        | 4.00 | 4     |

| е      | 0.050 BSC |        | 1.27 BSC    |      | -     |

| Н      | 0.2284    | 0.2440 | 5.80        | 6.20 | -     |

| h      | 0.0099    | 0.0196 | 0.25        | 0.50 | 5     |

| L      | 0.016     | 0.050  | 0.40        | 1.27 | 6     |

| Ν      | 8         |        | 8           |      | 7     |

| α      | 0°        | 8°     | 0°          | 8°   | -     |