### Features

Low-voltage and Standard-voltage Operation

- 1.8 (V<sub>CC</sub> = 1.8V to 5.5V)

- User-selectable Internal Organization - 1K: 128 x 8 or 64 x 16

- Three-wire Serial Interface

- 2 MHz Clock Rate (5V)

- Self-timed Write Cycle (5 ms max)

- High Reliability

- Endurance: 1 Million Write Cycles

- Data Retention: 100 Years

- 8-lead JEDEC PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin mini-MAP (MLP 2x3), 8-lead TSSOP and 8-ball dBGA2 Packages

- Die Sales: Wafer Form, Tape and Reel, and Bumped Wafers

# Description

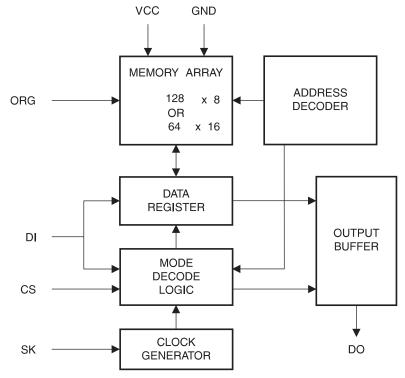

The AT93C46D provides 1024 bits of serial electrically erasable programmable readonly memory (EEPROM), organized as 64 words of 16 bits each (when the ORG pin is connected to VCC), and 128 words of 8 bits each (when the ORG pin is tied to ground). The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operations are essential. The AT93C46D is available in space-saving 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin mini-MAP (MLP 2x3), 8-lead TSSOP, and 8-lead dBGA2 packages.

The AT93C46D is enabled through the Chip Select pin (CS) and accessed via a three-wire serial interface consisting of Data Input (DI), Data Output (DO), and Shift Clock (SK). Upon receiving a Read instruction at DI, the address is decoded and the data is clocked out serially on the DO pin. The Write cycle is completely self-timed, and no separate Erase cycle is required before Write. The Write cycle is only enabled when the part is in the Erase/Write Enable state. When CS is brought high following the initiation of a Write cycle, the DO pin outputs the Ready/Busy status of the part.

The AT93C46D is available in 1.8 (1.8V to 5.5V) version.

### Table 0-1.Pin Configurations

Pin Name

CS SK DI

DO GND VCC ORG NC

| in Configurations |            | 8-lead SOIC        |                                                                                            | g                | 8-lead dBGA2            |             |

|-------------------|------------|--------------------|--------------------------------------------------------------------------------------------|------------------|-------------------------|-------------|

| Function          |            |                    |                                                                                            | -                |                         | _           |

| Chip Selec        | t          | CS [] 1<br>SK [] 2 | 8 🔲 V<br>7 🗌 N                                                                             | CC VCC<br>C NC   | 8 1 C<br>7 2 S          |             |

| Serial Data       | Clock      | DI 🔤 3<br>DO 🔄 4   |                                                                                            | RG ORG<br>ND GND | 6 3 D<br>5 4 D          | -           |

| Serial Data       | Input      |                    |                                                                                            | E                | Bottom View             |             |

| Serial Data       | Output     | 8-                 | lead PDIP                                                                                  | 8-lead Ultra T   | hin mini-MA             | P (MLP 2x3) |

| Ground            |            | CS □ 1             | 8 UVCC                                                                                     |                  |                         | cs          |

| Power Sup         | ply        | SK 🗆 2<br>DI 🗖 3   | 7 □ NC<br>6 □ ORC                                                                          |                  | 6 3                     | SK<br>DI    |

| Internal Or       | ganization |                    | 5 🗆 GNI                                                                                    |                  |                         | DO          |

| No Connec         | :t         |                    | 8-1                                                                                        | ead TSSOP        | Bottom View             | 1           |

|                   |            | -                  | $ \begin{array}{c} CS \square 1\\ SK \square 2\\ DI \square 3\\ DO \square 4 \end{array} $ |                  | VCC<br>NC<br>DRG<br>GND |             |

# Three-wire Serial EEPROM

1K (128 x 8 or 64 x 16)

# AT93C46D

#### **Absolute Maximum Ratings\*** 1.

| Γ | Operating Temperature55°C to +125°C                       |

|---|-----------------------------------------------------------|

|   | Storage Temperature65°C to +150°C                         |

|   | Voltage on Any Pin<br>with Respect to Ground1.0V to +7.0V |

|   | Maximum Operating Voltage 6.25V                           |

|   | DC Output Current 5.0 mA                                  |

Figure 1-1. **Block Diagram**

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

- Notes: 1. When the ORG pin is connected to VCC, the "x 16" organization is selected. When it is connected to ground, the "x 8" organization is selected. If the ORG pin is left unconnected and the application does not load the input beyond the capability of the internal 1 Meg ohm pullup, then the "x 16" organization is selected.

- 2. For the AT93C46D, if the "x 16" organization is the mode of choice and pin 6 (ORG) is left unconnected, Atmel® recommends using AT93C46E device. For more details, see the AT93C46E datasheet.

# AT93C46D

2

### Table 1-1.Pin Capacitance<sup>(1)</sup>

Applicable over recommended operating range from  $T_A = 25^{\circ}C$ , f = 1.0 MHz,  $V_{CC} = +1.8V$  (unless otherwise noted)

| Symbol           | Test Conditions                | Max | Units | Conditions     |

|------------------|--------------------------------|-----|-------|----------------|

| C <sub>OUT</sub> | Output Capacitance (DO)        | 5   | pF    | $V_{OUT} = 0V$ |

| C <sub>IN</sub>  | Input Capacitance (CS, SK, DI) | 5   | pF    | $V_{IN} = 0V$  |

Note: 1. This parameter is characterized and is not 100% tested.

#### Table 1-2.DC Characteristics

Applicable over recommended operating range from:  $T_{AI} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = +1.8V$  to +5.5V (unless otherwise noted)

| Symbol                          | Parameter           | Test Condition               | Test Condition            |                       | Тур  | Max                   | Unit |

|---------------------------------|---------------------|------------------------------|---------------------------|-----------------------|------|-----------------------|------|

| V <sub>CC1</sub>                | Supply Voltage      |                              |                           | 1.8                   |      | 5.5                   | V    |

| V <sub>CC2</sub>                | Supply Voltage      |                              |                           | 2.7                   |      | 5.5                   | V    |

| V <sub>CC3</sub>                | Supply Voltage      |                              |                           | 4.5                   |      | 5.5                   | V    |

| 1                               | Supply Current      |                              | READ at 1.0 MHz           |                       | 0.5  | 2.0                   | mA   |

| I <sub>CC</sub>                 | Supply Current      | $V_{\rm CC} = 5.0 V$         | WRITE at 1.0 MHz          |                       | 0.5  | 2.0                   | mA   |

| I <sub>SB1</sub>                | Standby Current     | V <sub>CC</sub> = 1.8V       | CS = 0V                   |                       | 0.4  | 1.0                   | μA   |

| I <sub>SB2</sub>                | Standby Current     | $V_{CC} = 2.7V$              | CS = 0V                   |                       | 6.0  | 10.0                  | μA   |

| I <sub>SB3</sub>                | Standby Current     | $V_{CC} = 5.0V$              | CS = 0V                   |                       | 10.0 | 15.0                  | μA   |

| I <sub>IL</sub>                 | Input Leakage       | $V_{IN} = 0V$ to $V_{CC}$    |                           |                       | 0.1  | 1.0                   | μA   |

| I <sub>OL</sub>                 | Output Leakage      | $V_{IN} = 0V$ to $V_{CC}$    |                           |                       | 0.1  | 1.0                   | μA   |

| V <sub>IL1</sub> <sup>(1)</sup> | Input Low Voltage   | $2.7V \leq V_{CC} \leq 5.5V$ |                           | -0.6                  |      | 0.8                   | V    |

| V <sub>IH1</sub> <sup>(1)</sup> | Input High Voltage  |                              |                           | 2.0                   |      | V <sub>CC</sub> + 1   |      |

| V <sub>IL2</sub> <sup>(1)</sup> | Input Low Voltage   |                              |                           | -0.6                  |      | V <sub>CC</sub> x 0.3 |      |

| V <sub>IH2</sub> <sup>(1)</sup> | Input High Voltage  | $1.8V \le V_{CC} \le 2.7V$   |                           | V <sub>CC</sub> x 0.7 |      | V <sub>CC</sub> + 1   | V    |

| V <sub>OL1</sub>                | Output Low Voltage  |                              | I <sub>OL</sub> = 2.1 mA  |                       |      | 0.4                   | V    |

| V <sub>OH1</sub>                | Output High Voltage | $2.7V \le V_{CC} \le 5.5V$   | I <sub>OH</sub> = -0.4 mA | 2.4                   |      |                       | V    |

| V <sub>OL2</sub>                | Output Low Voltage  |                              | I <sub>OL</sub> = 0.15 mA |                       |      | 0.2                   | V    |

| V <sub>OH2</sub>                | Output High Voltage | $1.8V \le V_{CC} \le 2.7V$   | I <sub>OH</sub> = −100 μA | $V_{CC} - 0.2$        |      |                       | V    |

Note: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

#### Table 1-3.AC Characteristics

Applicable over recommended operating range from  $T_{AI} = -40^{\circ}C$  to + 85°C,  $V_{CC} = +2.7V$  to +5.5V, CL = 1 TTL Gate and 100 pF (unless otherwise noted)

| Symbol                   | Parameter                     | Test Condition                                                                                                                    |                                                                                                                       | Min                | Тур | Мах                | Units        |

|--------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|--------------|

| f <sub>SK</sub>          | SK Clock<br>Frequency         | $\begin{array}{l} 4.5 V \leq V_{CC} \ \leq 5.5 V \\ 2.7 V \leq V_{CC} \ \leq 5.5 V \\ 1.8 V \leq V_{CC} \ \leq 5.5 V \end{array}$ |                                                                                                                       | 0<br>0<br>0        |     | 2<br>1<br>0.25     | MHz          |

| t <sub>sкн</sub>         | SK High Time                  | $\begin{array}{l} 4.5V \leq V_{CC} \ \leq 5.5V \\ 2.7V \leq V_{CC} \ \leq 5.5V \\ 1.8V \leq V_{CC} \ \leq 5.5V \end{array}$       |                                                                                                                       | 250<br>250<br>1000 |     |                    | ns           |

| t <sub>SKL</sub>         | SK Low Time                   | $\begin{array}{l} 4.5 V \leq V_{CC} \ \leq 5.5 V \\ 2.7 V \leq V_{CC} \ \leq 5.5 V \\ 1.8 V \leq V_{CC} \ \leq 5.5 V \end{array}$ |                                                                                                                       | 250<br>250<br>1000 |     |                    | ns           |

| t <sub>cs</sub>          | Minimum CS<br>Low Time        | $\begin{array}{l} 4.5 V \leq V_{CC} \ \leq 5.5 V \\ 2.7 V \leq V_{CC} \ \leq 5.5 V \\ 1.8 V \leq V_{CC} \ \leq 5.5 V \end{array}$ |                                                                                                                       | 250<br>250<br>1000 |     |                    | ns           |

| t <sub>CSS</sub>         | CS Setup Time                 | Relative to SK                                                                                                                    | $\begin{array}{c} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$ | 50<br>50<br>200    |     |                    | ns           |

| t <sub>DIS</sub>         | DI Setup Time                 | Relative to SK                                                                                                                    | $\begin{array}{l} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$ | 100<br>100<br>400  |     |                    | ns           |

| t <sub>CSH</sub>         | CS Hold Time                  | Relative to SK                                                                                                                    |                                                                                                                       | 0                  |     |                    | ns           |

| t <sub>DIH</sub>         | DI Hold Time                  | Relative to SK                                                                                                                    | $\begin{array}{l} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$ | 100<br>100<br>400  |     |                    | ns           |

| t <sub>PD1</sub>         | Output Delay to "1"           | AC Test                                                                                                                           | $\begin{array}{l} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$ |                    |     | 250<br>250<br>1000 | ns           |

| t <sub>PD0</sub>         | Output Delay to "0"           | AC Test                                                                                                                           | $\begin{array}{c} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$ |                    |     | 250<br>250<br>1000 | ns           |

| t <sub>SV</sub>          | CS to Status Valid            | AC Test                                                                                                                           | $\begin{array}{c} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$ |                    |     | 250<br>250<br>1000 | ns           |

| t <sub>DF</sub>          | CS to DO in High<br>Impedance | AC Test<br>CS = V <sub>IL</sub>                                                                                                   | $\begin{array}{c} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \\ 1.8V \leq V_{CC} \leq 5.5V \end{array}$ |                    |     | 100<br>150<br>400  | ns           |

| t <sub>WP</sub>          | Write Cycle Time              |                                                                                                                                   | $1.8V \leq V_{CC} \ \leq 5.5V$                                                                                        | 0.1                | 3   | 5                  | ms           |

| Endurance <sup>(1)</sup> | 5.0V, 25°C                    |                                                                                                                                   |                                                                                                                       | 1M                 |     |                    | Write Cycles |

Note: 1. This parameter is ensured by characterization.

4

## 4. AT93C46D Ordering Information

| Ordering Code                                       | Voltage | Package  | Operation Range                           |  |  |

|-----------------------------------------------------|---------|----------|-------------------------------------------|--|--|

| AT93C46D-PU (Bulk form only)                        | 1.8     | 8P3      |                                           |  |  |

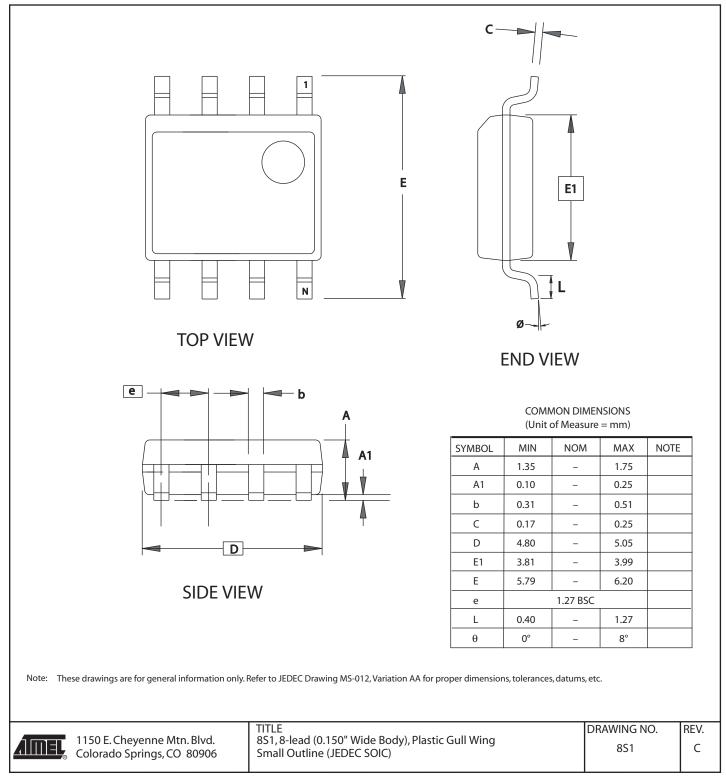

| AT93C46DN-SH-B <sup>(1)</sup> (NiPdAu Lead finish)  | 1.8     | 8S1      |                                           |  |  |

| AT93C46DN-SH-T <sup>(2)</sup> (NiPdAu Lead finish)  | 1.8     | 8S1      | Lead-free/Halogen-free/                   |  |  |

| AT93C46D-TH-B <sup>(1)</sup> (NiPdAu Lead finish)   | 1.8     | 8A2      | Industrial Temperature<br>(-40°C to 85°C) |  |  |

| AT93C46D-TH-T <sup>(2)</sup> (NiPdAu Lead finish)   | 1.8     | 8A2      | (-+0 0 10 00 0)                           |  |  |

| AT93C46DY6-YH-T <sup>(2)</sup> (NiPdAu Lead finish) | 1.8     | 8Y6      |                                           |  |  |

| AT93C46DU3-UU-T <sup>(2)</sup>                      | 1.8     | 8U3-1    |                                           |  |  |

| AT93C46D-W-11 <sup>(3)</sup>                        | 1.8     | Die Sale | Industrial<br>(–40°C to 85°C)             |  |  |

Notes: 1. "-B" denotes bulk

2. "-T" denotes tape and reel. SOIC = 4K per reel. TSSOP, Ultra Thin Mini MAP, and dBGA2 = 5K per reel.

3. Available in tape and reel, and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Please contact Serial Interface Marketing.

| Package Type |                                                                                                             |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| 8P3          | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                                     |  |  |  |

| 8S1          | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                                           |  |  |  |

| 8A2          | 8-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)                                              |  |  |  |

| 8U3-1        | 8-ball, Die Ball Grid Array Package (dBGA2)                                                                 |  |  |  |

| 8Y6          | 8-lead, 2.00 mm x 3.00 mm Body, 0.50mm Pitch, Ultra-Thin Mini-MAO, Dual No Lead Package. (DFN), (MLP 2x3mm) |  |  |  |

| Options      |                                                                                                             |  |  |  |

| -1.8         | Low Voltage (1.8V to 5.5V)                                                                                  |  |  |  |

### **8S1 - JEDEC SOIC**